Microprocesadores P1020NXN2HFB – MPU 800/400/667 ET NE r1.1

♠ Descripción del producto

| Atributo del producto | Valor del atributo |

| Fabricante: | NXP |

| Categoría de producto: | Microprocesadores - MPU |

| RoHS: | Detalles |

| Estilo de montaje: | SMD/SMT |

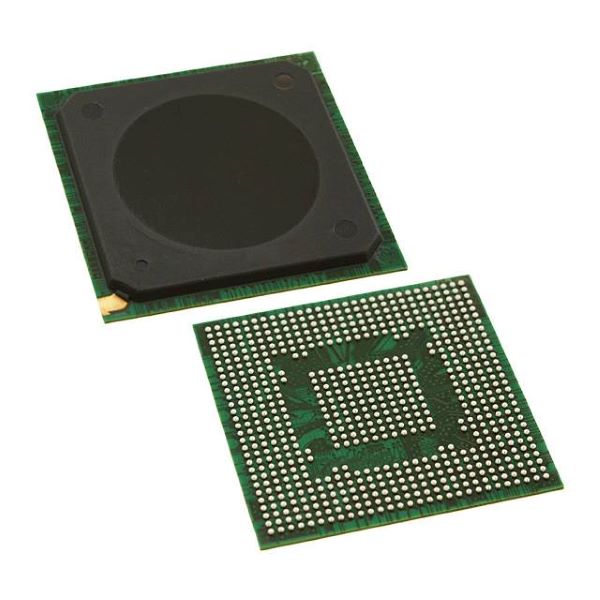

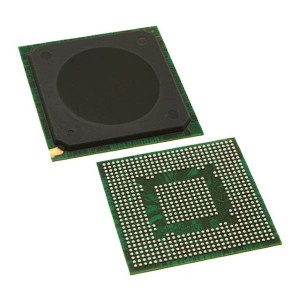

| Paquete/Caja: | TEPBGA-689 |

| Serie: | P1020 |

| Centro: | e500 |

| Número de núcleos: | 2 núcleos |

| Ancho del bus de datos: | 32 bits |

| Frecuencia máxima de reloj: | 800 MHz |

| Memoria de instrucciones de caché L1: | 2 x 32 kB |

| Memoria de datos caché L1: | 2 x 32 kB |

| Voltaje de suministro de funcionamiento: | 1 V |

| Temperatura mínima de funcionamiento: | - 40 °C |

| Temperatura máxima de funcionamiento: | + 125 C |

| Embalaje: | Bandeja |

| Marca: | Semiconductores NXP |

| Voltaje de E/S: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Tipo de instrucción: | Punto flotante |

| Tipo de interfaz: | Ethernet, I2C, PCIe, SPI, UART, USB |

| Instrucciones de caché L2 / Memoria de datos: | 256 kB |

| Tipo de memoria: | Caché L1/L2 |

| Sensible a la humedad: | Sí |

| Número de E/S: | 16 E/S |

| Serie de procesadores: | QorIQ |

| Tipo de producto: | Microprocesadores - MPU |

| Cantidad del paquete de fábrica: | 27 |

| Subcategoría: | Microprocesadores - MPU |

| Nombre comercial: | QorIQ |

| Temporizadores de vigilancia: | Sin temporizador de vigilancia |

| Número de pieza Alias: | 935310441557 |

| Peso unitario: | 5,247 gramos |

• Núcleos duales de 32 bits de alto rendimiento, basados en tecnología Power Architecture®:

– Direccionamiento físico de 36 bits

– Soporte de punto flotante de doble precisión

– Caché de instrucciones L1 de 32 Kbytes y caché de datos L1 de 32 Kbytes para cada núcleo

– Frecuencia de reloj de 533 MHz a 800 MHz

• Caché L2 de 256 KB con ECC. También configurable como SRAM y memoria caché.

• Tres controladores Ethernet de tres velocidades mejorados de 10/100/1000 Mbps (eTSEC)

– Aceleración TCP/IP, calidad de servicio y capacidades de clasificación

– Compatibilidad con IEEE® 1588

– Control de flujo sin pérdidas

– MII, RMII, RGMII, SGMII

• Interfaces de alta velocidad que admiten varias opciones de multiplexación:

– Cuatro SerDes de hasta 2,5 GHz/carril multiplexados entre controladores

– Dos interfaces PCI Express

– Dos interfaces SGMII

• Controlador USB de alta velocidad (USB 2.0)

– Soporte de host y dispositivo

– Interfaz de controlador de host mejorada (EHCI)

– Interfaz ULPI a PHY

• Controlador de host digital seguro mejorado (SD/MMC)

• Interfaz periférica serial mejorada (eSPI)

• Motor de seguridad integrado

– El soporte de protocolo incluye ARC4, 3DES, AES, RSA/ECC, RNG, SSL/TLS de una sola pasada

– Aceleración XOR

• Controlador de memoria SDRAM DDR2/DDR3 de 32 bits con soporte ECC

• Controlador de interrupciones programable (PIC) compatible con el estándar OpenPIC

• Un controlador DMA de cuatro canales

• Dos controladores I2 C, DUART, temporizadores

• Controlador de bus local mejorado (eLBC)

• TDM

• 16 señales de E/S de propósito general

• Rango de temperatura de unión de funcionamiento (Tj): 0–125 °C y –40 °C a 125 °C (especificación industrial)

• WB-TePBGA II de 31 × 31 mm y 689 pines (BGA de plástico con temperatura mejorada mediante unión por cable)