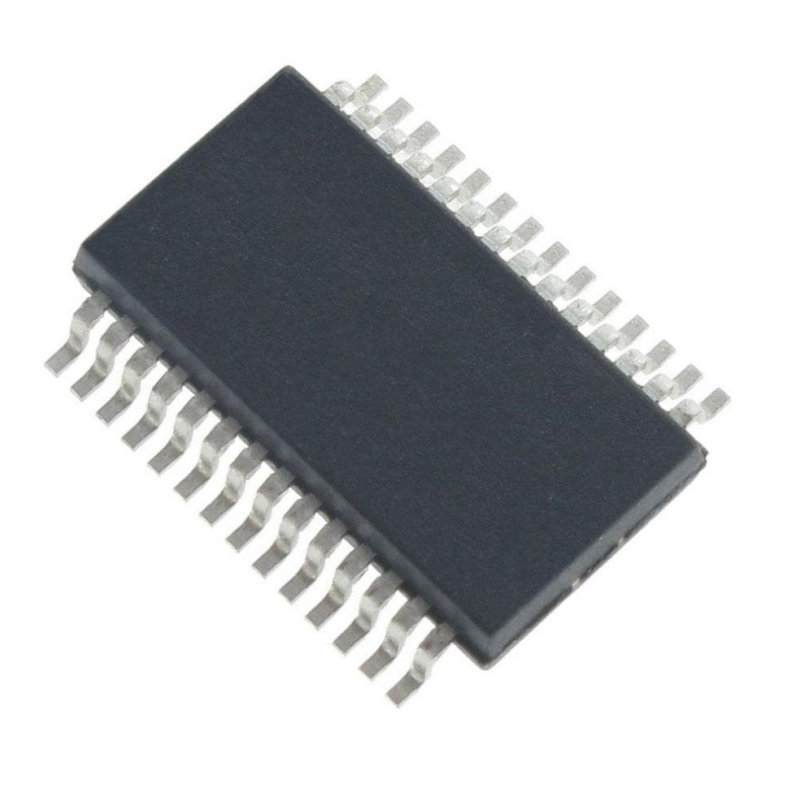

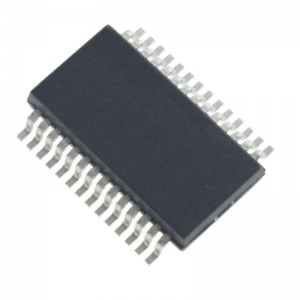

Microcontroladores PIC18F27Q84-I/SS de 8 bits, MCU CAN-FD, 128 KB de memoria Flash, 13 KB de RAM

♠ Descripción del producto

| Atributo del producto | Valor del atributo |

| Fabricante: | Pastilla |

| Categoría de producto: | Microcontroladores de 8 bits - MCU |

| RoHS: | Detalles |

| Serie: | PIC18F27Q84 |

| Estilo de montaje: | SMD/SMT |

| Paquete/Caja: | SSOP-28 |

| Centro: | PIC18 |

| Tamaño de la memoria del programa: | 128 kB |

| Ancho del bus de datos: | 8 bits |

| Resolución ADC: | 12 bits |

| Frecuencia máxima de reloj: | 64 MHz |

| Número de E/S: | 25 E/S |

| Tamaño de RAM de datos: | 12,5 kB |

| Tensión de alimentación - Mín.: | 1,8 V |

| Tensión de alimentación - Máx.: | 5,5 V |

| Temperatura mínima de funcionamiento: | - 40 °C |

| Temperatura máxima de funcionamiento: | + 85 C |

| Embalaje: | Tubo |

| Marca: | Tecnología de microchip / Atmel |

| Sensible a la humedad: | Sí |

| Producto: | MCU |

| Tipo de producto: | Microcontroladores de 8 bits - MCU |

| Cantidad del paquete de fábrica: | 47 |

| Subcategoría: | Microcontroladores - MCU |

| Nombre comercial: | FOTO |

♠ Microcontrolador de 28/40/44/48 pines, de bajo consumo y alto rendimiento con tecnología XLP

La familia de microcontroladores PIC18-Q84 está disponible en dispositivos de 28, 40, 44 y 48 pines para diversas aplicaciones automotrices e industriales. Los numerosos periféricos de comunicación de la familia, como la Red de Área de Controlador (CAN), la Interfaz Periférica Serie (SPI), el Circuito Interintegrado (I₂C) y dos Transmisores Receptores Asíncronos Universales (UART), admiten una amplia gama de protocolos de comunicación cableados e inalámbricos (mediante módulos externos) para aplicaciones inteligentes. Combinada con la integración de Periféricos Independientes del Núcleo (CIP), esta capacidad permite funciones para control de motores, alimentación, sensores, señales e interfaz de usuario. Además, esta familia incluye un Conversor Analógico-Digital (ADC) de 12 bits con extensiones de Computación y Conmutación de Contexto para el análisis automatizado de señales y reducir la complejidad de la aplicación.

• Arquitectura RISC optimizada para el compilador C

• Velocidad de funcionamiento:

– Entrada de reloj CC de 64 MHz

– Ciclo de instrucción mínimo de 62,5 ns

• Ocho controladores de acceso directo a memoria (DMA):

– Transferencias de datos a espacios SFR/GPR desde la memoria flash del programa, la EEPROM de datos o SFR/GPRespacios

– Tamaños de origen y destino programables por el usuario

– Transferencias de datos activadas por hardware y software

• Capacidad de interrupción vectorial:

– Prioridad alta/baja seleccionable

– Se corrigió la latencia de interrupción de tres ciclos de instrucción

– Dirección base de tabla vectorial programable

– Compatible con versiones anteriores de capacidades de interrupción

• Pila de hardware de 128 niveles de profundidad

• Reinicio de encendido de baja corriente (POR)

• Temporizador de encendido configurable (PWRT)

• Reinicio por caída de tensión (BOR)

• Opción BOR de bajo consumo (LPBOR)

• Temporizador de vigilancia con ventana (WWDT):

– Restablecimiento del watchdog en intervalos demasiado largos o demasiado cortos entre eventos de borrado del watchdog

– Selección de prescaler variable

– Selección de tamaño de ventana variable