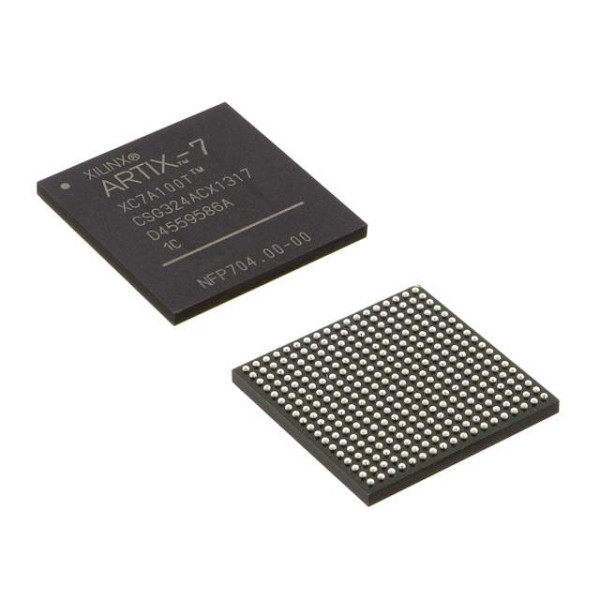

FPGA XC7A50T-2CSG324I: Matriz de puertas programables en campo XC7A50T-2CSG324I

♠ Descripción del producto

| Atributo del producto | Valor del atributo |

| Fabricante: | Xilinx |

| Categoría de producto: | FPGA - Matriz de puertas programables en campo |

| Serie: | XC7A50T |

| Número de elementos lógicos: | 52160 LE |

| Número de E/S: | 210 E/S |

| Tensión de alimentación - Mín.: | 0,95 V |

| Tensión de alimentación - Máx.: | 1,05 V |

| Temperatura mínima de funcionamiento: | - 40 °C |

| Temperatura máxima de funcionamiento: | + 100 C |

| Velocidad de datos: | - |

| Número de transceptores: | - |

| Estilo de montaje: | SMD/SMT |

| Paquete/Caja: | CSBGA-324 |

| Marca: | Xilinx |

| RAM distribuida: | 600 kbit |

| RAM de bloque integrada - EBR: | 2700 kbit |

| Sensible a la humedad: | Sí |

| Número de bloques de matriz lógica - LABs: | 4075 LABORATORIO |

| Voltaje de suministro de funcionamiento: | 1 V |

| Tipo de producto: | FPGA - Matriz de puertas programables en campo |

| Cantidad del paquete de fábrica: | 1 |

| Subcategoría: | Circuitos integrados lógicos programables |

| Nombre comercial: | Artix |

| Peso unitario: | 1 onza |

♠ Los FPGA de la serie 7 de Xilinx® comprenden cuatro familias de FPGA que abordan la gama completa de requisitos del sistema, desde aplicaciones de bajo costo, factor de forma pequeño, sensibles a los costos y de gran volumen hasta ancho de banda de conectividad de gama ultra alta, capacidad lógica y capacidad de procesamiento de señales para las aplicaciones de alto rendimiento más exigentes.

Las FPGAs de la serie 7 de Xilinx® comprenden cuatro familias que cubren todos los requisitos del sistema, desde aplicaciones de bajo coste, formato pequeño, de alto volumen y con precios competitivos hasta conectividad de gama alta, capacidad lógica y capacidad de procesamiento de señales para las aplicaciones de alto rendimiento más exigentes. Las FPGAs de la serie 7 incluyen:

Familia Spartan®-7: Optimizada para un bajo costo, el menor consumo y un alto rendimiento de E/S. Disponible en un empaque económico y de formato muy compacto para un espacio mínimo en la PCB.

Familia Artix®-7: Optimizada para aplicaciones de bajo consumo que requieren transceptores serie y alto rendimiento lógico y de DSP. Ofrece el menor costo total de lista de materiales para aplicaciones de alto rendimiento y sensibles a los costos.

• Familia Kintex®-7: optimizada para ofrecer la mejor relación precio-rendimiento con una mejora de 2X en comparación con la generación anterior, lo que permite una nueva clase de FPGA.

Familia Virtex®-7: Optimizada para el máximo rendimiento y capacidad del sistema, duplicando su rendimiento. Dispositivos de máxima capacidad gracias a la tecnología de interconexión de silicio apilado (SSI).

Los FPGAs de la serie 7, basados en una tecnología de proceso de puerta metálica de alta k (HKMG) de 28 nm, de alto rendimiento y bajo consumo (HPL), permiten un aumento incomparable en el rendimiento del sistema con 2,9 Tb/s de ancho de banda de E/S, 2 millones de capacidades de celdas lógicas y 5,3 TMAC/s de DSP, al tiempo que consumen un 50 % menos de energía que los dispositivos de la generación anterior para ofrecer una alternativa totalmente programable a los ASSP y ASIC.

• Lógica FPGA avanzada de alto rendimiento basada en tecnología de tabla de búsqueda (LUT) de 6 entradas reales configurable como memoria distribuida.

• RAM de bloque de doble puerto de 36 Kb con lógica FIFO incorporada para almacenamiento en búfer de datos en el chip.

• Tecnología SelectIO™ de alto rendimiento con soporte para interfaces DDR3 de hasta 1,866 Mb/s.

• Conectividad serial de alta velocidad con transceptores multi-gigabit integrados desde 600 Mb/s hasta velocidades máximas de 6,6 Gb/s hasta 28,05 Gb/s, ofreciendo un modo especial de bajo consumo, optimizado para interfaces de chip a chip.

• Una interfaz analógica configurable por el usuario (XADC) que incorpora convertidores analógico-digitales duales de 12 bits y 1 MSPS con sensores térmicos y de suministro en chip.

• Segmentos DSP con multiplicador de 25 x 18, acumulador de 48 bits y presumador para filtrado de alto rendimiento, incluido filtrado de coeficientes simétricos optimizado.

• Potentes mosaicos de gestión de reloj (CMT) que combinan bloques de bucle de enganche de fase (PLL) y administrador de reloj de modo mixto (MMCM) para lograr alta precisión y bajo jitter.

• Implemente rápidamente el procesamiento integrado con el procesador MicroBlaze™.

• Bloque integrado para PCI Express® (PCIe), para diseños de puerto raíz y punto final Gen3 de hasta x8.

• Amplia variedad de opciones de configuración, incluido soporte para memorias básicas, cifrado AES de 256 bits con autenticación HMAC/SHA-256 y detección y corrección de SEU integradas.

Encapsulado flip-chip de bajo costo, con conexión por cable, chip desnudo y alta integridad de señal, que facilita la migración entre miembros de la familia en el mismo encapsulado. Todos los encapsulados están disponibles sin plomo y algunos encapsulados con opción de plomo.

• Diseñado para un alto rendimiento y el menor consumo de energía con 28 nm, HKMG, proceso HPL, tecnología de proceso de voltaje de núcleo de 1,0 V y opción de voltaje de núcleo de 0,9 V para un consumo de energía aún menor.