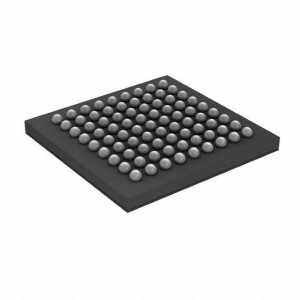

TMS320VC5509AZAY Procesadores y controladores de señales digitales: DSP, DSC Procesador de señales digitales de punto fijo 179-NFBGA -40 a 85

♠ Descripción del producto

| Atributo del producto | Valor de atributo |

| Fabricante: | Instrumentos Texas |

| Categoria de producto: | Procesadores y controladores de señales digitales - DSP, DSC |

| RoHS: | Detalles |

| Producto: | DSP |

| Serie: | TMS320VC5509A |

| Estilo de montaje: | SMD/SMT |

| Paquete/Estuche: | NFBGA-179 |

| Centro: | C55x |

| Numero de nucleos: | 1 núcleo |

| Frecuencia de reloj máxima: | 200 MHz |

| Memoria de instrucciones de caché L1: | - |

| Memoria de datos de caché L1: | - |

| Tamaño de la memoria del programa: | 64 KB |

| Tamaño de RAM de datos: | 256 KB |

| Voltaje de suministro operativo: | 1,6 V |

| Temperatura mínima de funcionamiento: | - 40C |

| Temperatura máxima de funcionamiento: | + 85C |

| Embalaje: | Bandeja |

| Marca: | Instrumentos Texas |

| Tipo de instrucción: | Punto fijo |

| Tipo de interfaz: | I2C |

| Sensible a la humedad: | Sí |

| Tipo de producto: | DSP - Procesadores y controladores de señales digitales |

| Cantidad del paquete de fábrica: | 160 |

| Subcategoría: | Procesadores y controladores integrados |

| Tensión de alimentación - Máx.: | 1,65 voltios |

| Tensión de alimentación - Mín.: | 1,55 voltios |

| Temporizadores de vigilancia: | Temporizador de vigilancia |

♠ Procesador de señal digital de punto fijo TMS320VC5509A

El procesador de señal digital (DSP) de punto fijo TMS320VC5509A se basa en el núcleo del procesador de CPU de generación TMS320C55x DSP.La arquitectura DSP C55x™ logra un alto rendimiento y bajo consumo de energía a través de un mayor paralelismo y un enfoque total en la reducción de la disipación de energía.La CPU admite una estructura de bus interna que se compone de un bus de programa, tres buses de lectura de datos, dos buses de escritura de datos y buses adicionales dedicados a la actividad periférica y DMA.Estos buses brindan la capacidad de realizar hasta tres lecturas de datos y dos escrituras de datos en un solo ciclo.En paralelo, el controlador DMA puede realizar hasta dos transferencias de datos por ciclo independientemente de la actividad de la CPU.

La CPU C55x proporciona dos unidades de multiplicación y acumulación (MAC), cada una con capacidad de multiplicación de 17 bits x 17 bits en un solo ciclo.Una unidad aritmética/lógica (ALU) central de 40 bits es compatible con una ALU adicional de 16 bits.El uso de las ALU está bajo el control del conjunto de instrucciones, lo que brinda la capacidad de optimizar la actividad paralela y el consumo de energía.Estos recursos se gestionan en la Unidad de Dirección (AU) y la Unidad de Datos (DU) de la UCP C55x.

La generación C55x DSP admite un conjunto de instrucciones de ancho de byte variable para mejorar la densidad del código.La Unidad de instrucción (IU) realiza búsquedas de programas de 32 bits desde la memoria interna o externa y pone en cola las instrucciones para la Unidad de programa (PU).La Unidad de programa decodifica las instrucciones, dirige las tareas a los recursos de AU y DU y administra la canalización completamente protegida.La capacidad de bifurcación predictiva evita vaciados de tubería en la ejecución de instrucciones condicionales.

Las funciones de entrada y salida de propósito general y el A/D de 10 bits proporcionan pines suficientes para estado, interrupciones y E/S de bits para LCD, teclados e interfaces de medios.La interfaz paralela opera en dos modos, ya sea como esclavo de un microcontrolador usando el puerto HPI o como una interfaz de medios paralela usando la EMIF asíncrona.Los medios seriales son compatibles a través de dos periféricos MultiMedia Card/Secure Digital (MMC/SD) y tres McBSP.

El conjunto de periféricos 5509A incluye una interfaz de memoria externa (EMIF) que proporciona acceso sin colas a memorias asíncronas como EPROM y SRAM, así como a memorias de alta velocidad y alta densidad como DRAM síncrona.Los periféricos adicionales incluyen Universal Serial Bus (USB), reloj en tiempo real, temporizador de vigilancia, interfaz I2C multimaestro y esclavo.Tres puertos seriales con búfer multicanal full-duplex (McBSP) proporcionan una interfaz sin cola para una variedad de dispositivos seriales estándar de la industria y comunicación multicanal con hasta 128 canales habilitados por separado.La interfaz de puerto de host mejorada (HPI) es una interfaz paralela de 16 bits que se utiliza para brindar acceso al procesador de host a 32 000 bytes de memoria interna en el 5509A.El HPI se puede configurar en modo multiplexado o no multiplexado para proporcionar una interfaz sin cola a una amplia variedad de procesadores host.El controlador DMA proporciona movimiento de datos para seis contextos de canal independientes sin intervención de la CPU, proporcionando un rendimiento DMA de hasta dos palabras de 16 bits por ciclo.También se incluyen dos temporizadores de uso general, hasta ocho pines de E/S de uso general (GPIO) dedicados y generación de reloj de bucle de enganche de fase digital (DPLL).

El 5509A es compatible con el premiado eXpressDSP™ de la industria, el entorno de desarrollo integrado (IDE) Code Composer Studio™, DSP/BIOS™, el algoritmo estándar de Texas Instruments y la red de terceros más grande de la industria.El IDE de Code Composer Studio presenta herramientas de generación de código que incluyen un compilador C y un vinculador visual, un simulador, controladores de dispositivo de emulación RTDX™, XDS510™ y módulos de evaluación.El 5509A también es compatible con la biblioteca C55x DSP, que cuenta con más de 50 núcleos de software básicos (filtros FIR, filtros IIR, FFT y varias funciones matemáticas), así como bibliotecas de compatibilidad con chips y placas.

El núcleo TMS320C55x DSP se creó con una arquitectura abierta que permite agregar hardware específico de la aplicación para aumentar el rendimiento en algoritmos específicos.Las extensiones de hardware del 5509A logran el equilibrio perfecto entre el rendimiento de funciones fijas y la flexibilidad programable, al mismo tiempo que logran un bajo consumo de energía y un costo que tradicionalmente ha sido difícil de encontrar en el mercado de procesadores de video.Las extensiones permiten que el 5509A brinde un rendimiento de códec de video excepcional con más de la mitad de su ancho de banda disponible para realizar funciones adicionales como conversión de espacio de color, operaciones de interfaz de usuario, seguridad, TCP/IP, reconocimiento de voz y conversión de texto a voz.Como resultado, un solo DSP 5509A puede alimentar la mayoría de las aplicaciones de video digital portátiles con margen de procesamiento de sobra.Para obtener más información, consulte la Referencia del programador de extensiones de hardware para aplicaciones de imagen/video TMS320C55x (documento número SPRU098).Para obtener más información sobre el uso de la biblioteca de procesamiento de imágenes DSP, consulte la referencia del programador de la biblioteca de procesamiento de imágenes/video TMS320C55x (número de literatura SPRU037).

• Procesador de señal digital de punto fijo TMS320C55x™ de bajo consumo y alto rendimiento

− Tiempo de ciclo de instrucción de 9,26, 6,95 y 5 ns

− Frecuencia de reloj de 108, 144 y 200 MHz

− Una/dos instrucciones ejecutadas por ciclo

− Multiplicadores duales [hasta 400 millones de acumulaciones multiplicadas por segundo (MMACS)]

− Dos unidades aritméticas/lógicas (ALU)

− Tres buses internos de lectura de datos/operandos y dos buses internos de escritura de datos/operandos

• RAM en chip de 128 000 x 16 bits, compuesta por:

− 64K Bytes de RAM de acceso dual (DARAM) 8 bloques de 4K × 16 bits

− 192K Bytes de RAM de acceso único (SARAM) 24 bloques de 4K × 16 bits

• 64 000 bytes de ROM en chip de estado de una espera (32 000 × 16 bits)

• Espacio máximo de memoria externa direccionable de 8M × 16 bits (DRAM síncrona)

• Memoria de bus paralelo externo de 16 bits compatible con:

− Interfaz de memoria externa (EMIF) con capacidades GPIO e interfaz sin pegamento para:

− RAM estática asíncrona (SRAM)

− EPROM asíncrona

− DRAM síncrona (SDRAM)

− Interfaz de puerto de host mejorada paralela (EHPI) de 16 bits con capacidades GPIO

• Control programable de bajo consumo de seis dominios funcionales de dispositivos

• Lógica de emulación basada en escaneo en chip

• Periféricos en chip

− Dos temporizadores de 20 bits

− Temporizador de vigilancia

− Controlador de acceso directo a memoria (DMA) de seis canales

− Tres puertos serie que admiten una combinación de:

− Hasta 3 puertos serie con búfer multicanal (McBSP)

− Hasta 2 interfaces de tarjeta MultiMedia/Secure Digital

− Generador de reloj de bucle de bloqueo de fase programable

− Siete (LQFP) u ocho (BGA) pines de E/S de propósito general (GPIO) y un pin de salida de propósito general (XF)

− Puerto esclavo USB de velocidad completa (12 Mbps) que admite transferencias masivas, de interrupción e isócronas

− Interfaz Multi-Maestro y Esclavo de Circuito Inter-Integrado (I2C)

−Reloj en tiempo real (RTC) con entrada de cristal, dominio de reloj separado, fuente de alimentación separada

− A/D de aproximación sucesiva de 10 bits de 4 canales (BGA) o 2 canales (LQFP)

• Lógica de exploración de límites IEEE Std 1149.1† (JTAG)

• Paquetes:

− Paquete plano cuádruple de perfil bajo de 144 terminales (LQFP) (sufijo PGE)

− 179-Terminal MicroStar BGA™ (matriz de rejilla esférica) (sufijo GHH)

− MicroStar BGA™ sin plomo de 179 terminales (matriz de rejilla esférica) (sufijo ZHH)

• Núcleo de 1,2 V (108 MHz), 2,7 V – 3,6 VI/O

• Núcleo de 1,35 V (144 MHz), 2,7 V – 3,6 VI/O

• Núcleo de 1,6 V (200 MHz), 2,7 V – 3,6 VI/O

• Sistema híbrido, eléctrico y de tren de potencia (EV/HEV)

– Sistema de gestión de batería (BMS)

– Cargador a bordo

– Inversor de tracción

– Convertidor CC/CC

– Arrancador/generador