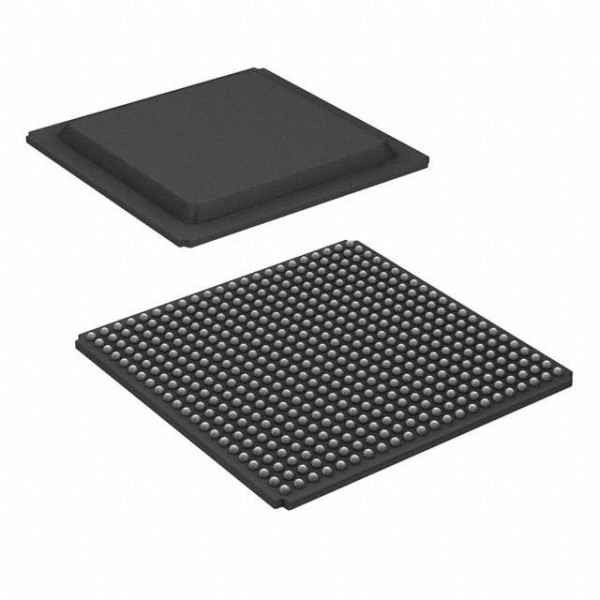

Matriz de puertas programables en campo XC6SLX75-2FGG484C

♠ Descripción del producto

| Atributo del producto | Valor del atributo |

| Fabricante: | Xilinx |

| Categoría de producto: | FPGA - Matriz de puertas programables en campo |

| RoHS: | Detalles |

| Serie: | XC6SLX75 |

| Número de elementos lógicos: | 74637 LE |

| Número de E/S: | 280 E/S |

| Tensión de alimentación - Mín.: | 1,14 V |

| Tensión de alimentación - Máx.: | 1,26 V |

| Temperatura mínima de funcionamiento: | 0 °C |

| Temperatura máxima de funcionamiento: | + 85 C |

| Velocidad de datos: | - |

| Número de transceptores: | - |

| Estilo de montaje: | SMD/SMT |

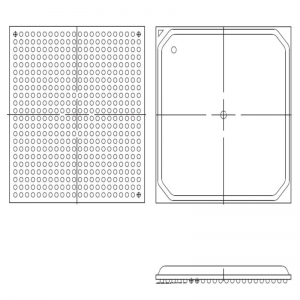

| Paquete/Caja: | FCBGA-484 |

| Marca: | Xilinx |

| RAM distribuida: | 692 kbit |

| RAM de bloque integrada - EBR: | 3096 kbit |

| Frecuencia máxima de funcionamiento: | 1080 MHz |

| Sensible a la humedad: | Sí |

| Número de bloques de matriz lógica - LABs: | 5831 LAB |

| Voltaje de suministro de funcionamiento: | 1,2 V |

| Tipo de producto: | FPGA - Matriz de puertas programables en campo |

| Cantidad del paquete de fábrica: | 1 |

| Subcategoría: | Circuitos integrados lógicos programables |

| Nombre comercial: | espartano |

| Peso unitario: | 1.662748 onzas |

♠ Descripción general de la familia Spartan-6

La familia Spartan®-6 ofrece capacidades líderes de integración de sistemas con el menor costo total para aplicaciones de alto volumen. Esta familia de trece componentes ofrece densidades expandidas, de 3840 a 147 443 celdas lógicas, con la mitad del consumo de energía que las familias Spartan anteriores y una conectividad más rápida y completa. Basada en una tecnología consolidada de proceso de cobre de bajo consumo de 45 nm que ofrece el equilibrio óptimo entre costo, potencia y rendimiento, la familia Spartan-6 ofrece una nueva lógica de tabla de búsqueda (LUT) de doble registro y 6 entradas, más eficiente, y una amplia selección de bloques integrados a nivel de sistema. Estos incluyen bloques de RAM de 18 Kb (2 x 9 Kb), porciones DSP48A1 de segunda generación, controladores de memoria SDRAM, bloques de administración de reloj de modo mixto mejorados, tecnología SelectIO™, bloques transceptores seriales de alta velocidad optimizados en energía, bloques de puntos finales compatibles con PCI Express®, modos avanzados de administración de energía a nivel de sistema, opciones de configuración de detección automática y seguridad IP mejorada con protección AES y Device DNA.

Estas características ofrecen una alternativa programable de bajo coste a los productos ASIC personalizados, con una facilidad de uso sin precedentes. Los FPGA Spartan-6 ofrecen la mejor solución para diseños lógicos de alto volumen, diseños DSP orientados al consumidor y aplicaciones embebidas con precios competitivos. Los FPGA Spartan-6 son la base de silicio programable para las Plataformas de Diseño Dirigido (TDD), que ofrecen componentes integrados de software y hardware que permiten a los diseñadores centrarse en la innovación desde el inicio del ciclo de desarrollo.

• Familia Spartan-6:

- FPGA Spartan-6 LX: lógica optimizada

- FPGA Spartan-6 LXT: Conectividad serial de alta velocidad

• Diseñado para bajo costo

- Múltiples bloques integrados eficientes

- Selección optimizada de estándares de E/S

- Almohadillas escalonadas

- Paquetes de plástico unidos con alambre de gran volumen

• Baja potencia estática y dinámica

- Proceso de 45 nm optimizado para lograr un bajo costo y consumo de energía.

- Modo de apagado por hibernación para consumo de energía cero

- El modo de suspensión mantiene el estado y la configuración con activación de múltiples pines y mejora del control.

- Voltaje de núcleo de 1,0 V de menor potencia (FPGAs LX, -1L solamente)

- Voltaje de núcleo de 1,2 V de alto rendimiento (FPGAs LX y LXT, grados de velocidad -2, -3 y -3N)

• Bancos de interfaz SelectIO™ multivoltaje y multiestándar

- Velocidad de transferencia de datos de hasta 1080 Mb/s por E/S diferencial

- Unidad de salida seleccionable, hasta 24 mA por pin

- Estándares y protocolos de 3,3 V a 1,2 VI/O

- Interfaces de memoria HSTL y SSTL de bajo costo

- Cumplimiento de intercambio en caliente

- Velocidades de respuesta de E/S ajustables para mejorar la integridad de la señal

• Transceptores seriales GTP de alta velocidad en los FPGA LXT

- Hasta 3,2 Gb/s

- Interfaces de alta velocidad que incluyen: Serial ATA, Aurora, Ethernet 1G, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort y XAUI

• Bloque de punto final integrado para diseños PCI Express (LXT)

• Soporte de tecnología PCI® de bajo costo compatible con la especificación de 33 MHz, 32 y 64 bits.

• Rebanadas DSP48A1 eficientes

- Aritmética de alto rendimiento y procesamiento de señales

- Multiplicador rápido de 18 x 18 y acumulador de 48 bits

- Capacidad de canalización y conexión en cascada

- Pre-sumador para ayudar a las aplicaciones de filtrado

• Bloques de controlador de memoria integrado

- Compatibilidad con DDR, DDR2, DDR3 y LPDDR

- Velocidades de datos de hasta 800 Mb/s (ancho de banda máximo de 12,8 Gb/s)

- Estructura de bus multipuerto con FIFO independiente para reducir los problemas de sincronización del diseño

• Abundantes recursos lógicos con mayor capacidad lógica

- Compatibilidad con registro de desplazamiento opcional o RAM distribuida

- Las LUT de 6 entradas eficientes mejoran el rendimiento y minimizan el consumo de energía

- LUT con flip-flops duales para aplicaciones centradas en tuberías

• Bloque de RAM con una amplia gama de granularidad

- RAM de bloque rápido con habilitación de escritura de bytes

- Bloques de 18 Kb que se pueden programar opcionalmente como dos RAM de bloque independientes de 9 Kb

• Mosaico de administración del reloj (CMT) para un rendimiento mejorado

- Bajo nivel de ruido, sincronización flexible

- Los administradores de reloj digital (DCM) eliminan la desviación del reloj y la distorsión del ciclo de trabajo

- Bucles de enganche de fase (PLL) para reloj de baja fluctuación

- Síntesis de frecuencia con multiplicación, división y desplazamiento de fase simultáneos

- Dieciséis redes de reloj global de baja asimetría

• Configuración simplificada, compatible con estándares de bajo costo

- Configuración de detección automática de 2 pines

- Amplia compatibilidad con SPI de terceros (hasta x4) y flash NOR

- Xilinx Platform Flash con JTAG y rica en funciones

- Compatibilidad con MultiBoot para actualización remota con múltiples flujos de bits, utilizando protección de vigilancia

• Seguridad mejorada para la protección del diseño

- Identificador único de ADN del dispositivo para la autenticación del diseño

- Cifrado de flujo de bits AES en los dispositivos más grandes

• Procesamiento integrado más rápido con procesador suave MicroBlaze™ mejorado y de bajo costo

• Diseños de referencia e IP líderes en la industria